It is clear that the VR application area seems to be subject to some limitations, that is, entertainment. Most VRs use resources in games, movies, and other entertainment. In fact, VR is not so superficial.

As a leader in the next generation of innovative technology, how can VR be just entertainment? SyncThink has announced that Indiana University will use the company's technology to study the effects of sub-concussive on the head.

Although eye tracking technology has not yet been implemented on consumer virtual reality head-mounted displays (HMDs), it is considered one of the most promising technologies in virtual reality. SyncThink, a company specializing in neuroscience technology, received another patent from the US Patent and Trademark Licensing Authority to add eye tracking to VR heads.

The project was conducted by assistant professor Keisuke Kawata. Kawata's project aims to fill the gap in the study of the impact of the sub-cerebral concussion head, and EYE-SYNC should provide a valuable indicator for his study of eye movement disturbances after sub-convex impacts. In addition, the SyncThink team will assist Kawata in completing the research and providing technical and analytical assistance.

This study helps to ensure the safety of athletes and to help detect repetitive sub-shock head impacts after subclinical nerve injury. The project will begin in February 2017. We look forward to new advances in other areas brought about by vr technology.

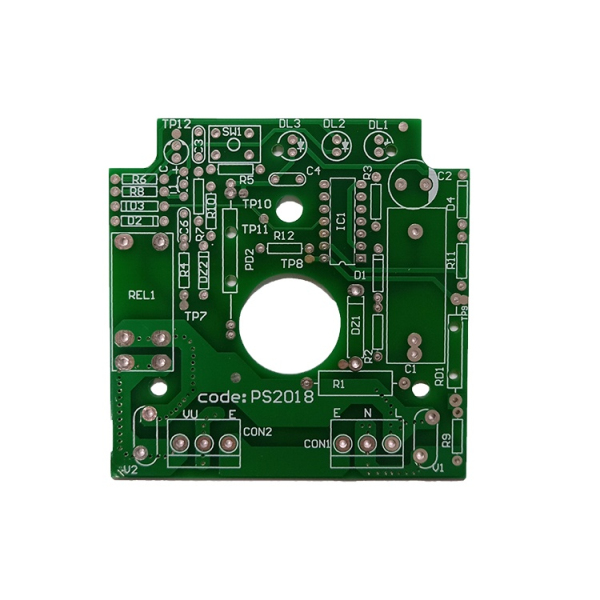

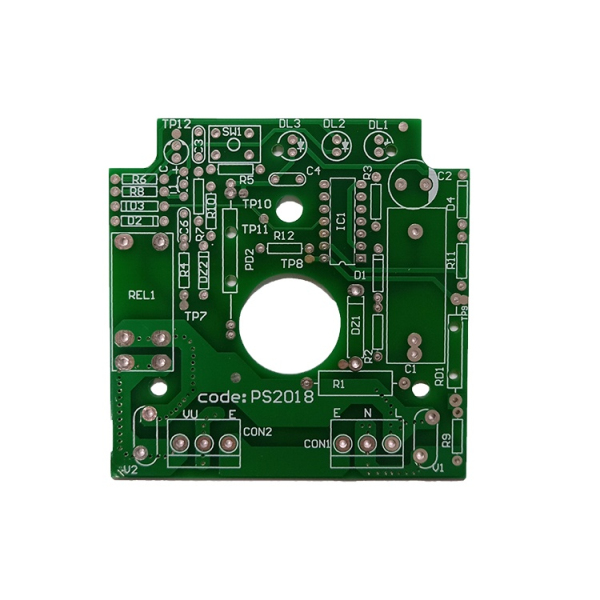

Characteristic Impedance PCB

How do you do impedance matching in PCB?

In high-speed PCB design, impedance matching must be considered in order to prevent reflections. However, because the PCB processing technology limits the impedance continuity and simulation cannot be simulated, how to consider this issue in the design of the schematic? In addition, regarding the IBIS model, I wonder where a more accurate IBIS model library can be provided. Most of the libraries we downloaded from the Internet are not very accurate, which greatly affects the reference of the simulation.

When designing high-speed PCB circuits, impedance matching is one of the design elements. The impedance value has an absolute relationship with the wiring method, such as walking on the surface layer (microstrip) or inner layer (stripline/double stripline), distance from the reference layer (power layer or ground layer), wiring width, PCB material, etc. Both will affect the characteristic impedance value of the trace. That is to say, the impedance value can only be determined after wiring. Generally, simulation software cannot take into account some wiring conditions with discontinuous impedance due to the limitation of the circuit model or the mathematical algorithm used. At this time, only some terminators (termination), such as series resistance, can be reserved on the schematic diagram. Alleviate the effect of discontinuity in trace impedance. The real solution to the problem is to try to avoid impedance discontinuities when wiring. The accuracy of the IBIS model directly affects the simulation results. Basically, IBIS can be regarded as the electrical characteristics data of the equivalent circuit of the actual chip I/O buffer, which can generally be obtained by conversion of the SPICE model (measurement can also be used, but there are more restrictions), and the SPICE data and chip manufacturing have absolute Therefore, the SPICE data of the same device provided by different chip manufacturers is different, and the data in the converted IBIS model will also vary accordingly. In other words, if manufacturers A`s devices are used, only they have the ability to provide accurate model data for their devices, because no one else knows better than them what process their devices are made of. If the IBIS provided by the manufacturer is inaccurate, the fundamental solution can only be to continuously ask the manufacturer to improve.

In high-speed PCB design, the software we use is only to check the EMC and EMI rules that have been set, but from which aspects should the designer consider the EMC and EMI rules? How to set up rules?

Generally, EMI/EMC design needs to consider both radiated and conducted aspects. The former belongs to the higher frequency part (<30MHz) and the latter is the lower frequency part (<30MHz). So you can't just pay attention to the high frequency and ignore the low frequency part. A good EMI/EMC design must consider the location of the device at the beginning of the layout. The arrangement of the PCB stack, the important connection method, the selection of the device, etc. If there is no better arrangement beforehand, it will be half the effort and increase the cost if it is resolved afterwards. For example, the location of the clock generator should not be as close as possible to the external connector. High-speed signals should go to the inner layer as much as possible. Pay attention to the characteristic impedance matching and the continuity of the reference layer to reduce the slew rate of the signal pushed by the reflective device. When choosing a decoupling/bypass capacitor, pay attention to whether its frequency response meets the requirements to reduce noise on the power plane. In addition, pay attention to the return path of the high-frequency signal current to make the loop area as small as possible (that is, the loop impedance as small as possible) to reduce radiation. The ground can also be divided to control the range of high-frequency noise. Finally, properly select the grounding point between the PCB and the case.

Characteristic Impedance Cpb,Controlled Impedance Pcb,Characteristic Impedance Pcb,Heavy Copper Board

HAODA ELECTRONIC CO.,LIMITED , https://www.pcbhdi.com