Software radio (SDR) architecture has always been considered a panacea for base station development, and as its ability to adapt to new protocols continues to increase, software radio architecture has been regarded by some designers as important to support multiple wireless protocols in a single infrastructure design solution.

Until recently, software radio was still only a blueprint for most communication system designers, but this situation is rapidly improving. As the 3G wireless business is approaching, designers have become more interested in implementing software radio structures in infrastructure design.

Implement Software Radio

Traditional wireless infrastructure design can be implemented using a combination of ASIC, DSP, and FPGA devices. In these designs, ASICs and FPGAs are usually responsible for handling advanced coding mechanisms, such as Reed Solomon coding, Viterbi coding, and Rake receivers, while DSPs are responsible for voice coding and other voice processing tasks.

In the process of shifting from traditional wireless architecture design to software radio design, the functional division between DSP, FPGA and ASIC has also changed. ASICs gradually provide more programmable functions, while DSPs and FPGAs begin to have the traditional processing functions of ASICs, and the boundaries between the three are becoming increasingly blurred. Therefore, when designers design software radios, they find it difficult to divide the functional boundaries between ASIC, DSP, and FPGA.

Now designers must expend considerable effort to weigh the following questions: Can the functions traditionally implemented by ASICs be better implemented by FPGA or DSP? Or is it more appropriate to implement functions traditionally implemented by DSP by FPGA or ASIC? Therefore, the core of the problem is how to formulate the correct selection criteria and effectively evaluate each treatment plan.

Criteria selection

Before choosing any criteria, it is necessary to give a precise definition of software radio. Throughout the backplane, developers can give many different definitions of the structure of the software radio, but this article will use the method of the software radio forum (RForum.org) to define the software radio as "in a large frequency range, can Software-controlled radios are required for many existing modulation standards, broadband and narrowband operations, communication security functions (such as frequency hopping), and signal waveforms that are currently in existence and will appear in the future. "

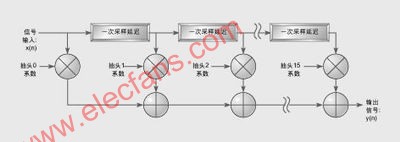

Historically, digital wireless systems have been implemented in jet aircraft designed with a single space interface standard. This design uses arbitrary programmable devices to evaluate the system based on cost considerations (see Figure 1). In software radio, each of the main functional devices of the radio (including radio frequency transceivers) has the characteristics of reconfiguration in the air to support multiple space interface standards.

The reconfigurable feature requires software radio to change the criteria that designers need to consider. Since pure processing power occupies a dominant position in the current 2G wireless environment, programmable functions have gradually become the focus of software radio design and application.

In short, when choosing ASIC, FPGA or DSP, designers should consider the following five important selection criteria. 1. Programmability: For all target space interface standards, the device can be reconfigured to perform the desired function. 2. Integration: The ability to integrate multiple functions on a single device, thereby reducing the specifications of the digital wireless subsystem and reducing hardware complexity. 3. Development cycle: the time to develop, implement and test the digital wireless functions of the specified device. 4. Performance: The ability of the device to complete the specified function within the required time. 5. Power: The power utilization rate of the device to complete the specified function.

Any of the above criteria will have a direct impact on the designer's choice of DSP, ASIC or FPGA.

Programmability

DSP and FPGA can be easily reconfigured to implement various functions of software radio design. Although the existing communication ASIC can provide better performance at a lower cost, the programmable capability provided is very limited.

The key question is whether there is a digital wireless product suitable for specific requirements among many wireless ASICs. In the pure software radio structure, obviously no ASIC has such a function, but in fact, only a few digital wireless designs require such high flexibility. Therefore, the key step in software radio product development is to determine the programmable features required for each function of the system, and to determine whether the existing ASIC can provide this function.

Determining the processing functions of the device can be illustrated by the structure of a base transceiver station that supports both W-CDMA and GSM. Because W-CDMA uses spread spectrum communication technology, many users can share a radio frequency (RF) channel. Between 1,920 to 1,980 MHz in the uplink and 2,110 to 2,170 MHz in the downlink, the W-CDMA signal occupies a bandwidth of 5 MHz in each channel.

On the other hand, in each radio frequency channel of the GSM system, the narrowband TDMA technology generally supports only 8 users. Between uplink 890 to 915 MHz and downlink 935 to 960 MHz, each channel of narrow-band TDMA occupies a 200 kHz bandwidth.

In order to effectively account for the differences between the above standards in the software radio architecture, the digital up converter and down converter of the intermediate frequency (IF) processor must provide programmable channel selection, filter configuration, and sampling ratio adjustment. Intersil, Graychip, and Analog Devices' new multi-standard digital transceiver ASICs can all provide many programmable features.

For example, Graychip's GC4016 digital down converter can be reconfigured as a 4-channel narrow-band down converter with a maximum available baseband bandwidth of 2.25 MHz per channel, or as a single-channel broadband down converter with a maximum available baseband bandwidth of 9 MHz. In addition, the GC4016 will also support user-programmable baseband filters and resamplers in each channel, which makes the device suitable for intermediate frequency processing of specified structures.

Yellow Box Candle export to Ghana market. 38G Yellow Box Candle is the most popular in Ghana. It is Bright Candle . The feature of Yellow Glass Jar Candle is White, Stick, wax Candle. The package of Yellow Scented Candle With Box is 8pcs/box 30boxes/ctn . Yellow Glass Jar Candle's sample are free, you just pay expree fee. The good quality and best price of Yellow Box Candle will be satisfited with you. About brand,we can do your own brand.

Welcome to order.

Yellow Box Candle

Yellow Box Candle,Yellow Glass Jar Candle,Yellow Scented Candle With Box,38G Yellow Box Candle

Shijiazhuang Zhongya Candle Co,. Ltd. , https://www.zycandlefactory.com