Embedded systems often rely on multitasking to manage operations and control. To ensure smooth functioning, these systems must implement mechanisms that prevent tasks from interfering with each other, especially when it comes to accessing shared resources. This is crucial for maintaining system stability and security. Embedded systems typically include specialized hardware designed to monitor and restrict access to critical resources, ensuring proper ownership and control. Tasks must follow predefined rules set by the operating environment, granting specific privileges at the hardware level for managing and monitoring resource usage. Unlike software-based approaches, hardware-enabled proactive monitoring offers a more robust solution for preventing unauthorized access between tasks.

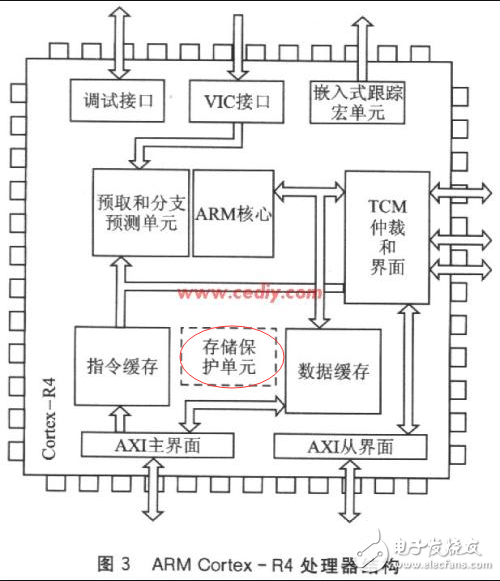

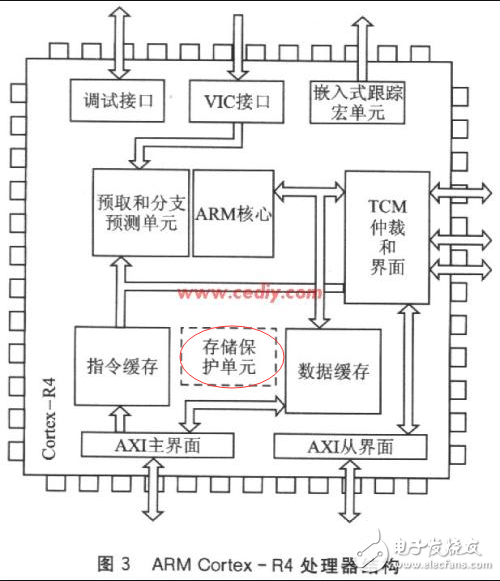

The Memory Protection Unit (MPU) is a key component in ARM-based systems, providing effective memory protection by defining and controlling access to different memory regions. It plays a vital role in securing system resources and ensuring that only authorized tasks can access specific areas of memory.

**MPU Functionality**

**(1) Memory Area Protection**

The MPU in ARM processors organizes memory into "regions" or domains. Each domain is an attribute associated with a specific memory area, stored in registers of the coprocessor CP15. Typically, there are up to eight domains, numbered from 0 to 7. The size and starting address of each domain are defined in register c6 of CP15. The size can be any power of two, ranging from 4 KB to 4 GB, and the starting address must be aligned with the domain size. For example, a 4 KB domain must start at an address that is a multiple of 4 KB.

**(2) Overlapping Protected Areas**

Some memory spaces can be assigned to multiple domains, allowing for overlapping regions. In such cases, priority levels can be set to determine which domain takes precedence. This flexibility makes overlapping domains more versatile than non-overlapping ones when assigning access rights.

**(3) Access Rights Control**

The operating system can define various attributes for each domain, including access permissions, cache settings, and write-back policies. Depending on the current processor mode—whether it's privileged or user mode—the MPU enforces different access rules. When a task tries to access a memory region, the MPU checks the access rights against the current mode. If the request is invalid, an exception is triggered.

**(4) Exception Handling**

When an invalid memory access occurs, the MPU sends an exception signal to the processor core. The core then jumps to the corresponding exception handler, which determines whether the error was a prefetch abort or a data abort and executes the appropriate service routine.

**How the MPU Works**

**(1) Memory Area Protection**

The MPU in ARM processors organizes memory into "regions" or domains. Each domain is an attribute associated with a specific memory area, stored in registers of the coprocessor CP15. Typically, there are up to eight domains, numbered from 0 to 7. The size and starting address of each domain are defined in register c6 of CP15. The size can be any power of two, ranging from 4 KB to 4 GB, and the starting address must be aligned with the domain size. For example, a 4 KB domain must start at an address that is a multiple of 4 KB.

**(2) Overlapping Protected Areas**

Some memory spaces can be assigned to multiple domains, allowing for overlapping regions. In such cases, priority levels can be set to determine which domain takes precedence. This flexibility makes overlapping domains more versatile than non-overlapping ones when assigning access rights.

**(3) Access Rights Control**

The operating system can define various attributes for each domain, including access permissions, cache settings, and write-back policies. Depending on the current processor mode—whether it's privileged or user mode—the MPU enforces different access rules. When a task tries to access a memory region, the MPU checks the access rights against the current mode. If the request is invalid, an exception is triggered.

**(4) Exception Handling**

When an invalid memory access occurs, the MPU sends an exception signal to the processor core. The core then jumps to the corresponding exception handler, which determines whether the error was a prefetch abort or a data abort and executes the appropriate service routine.

**How the MPU Works**

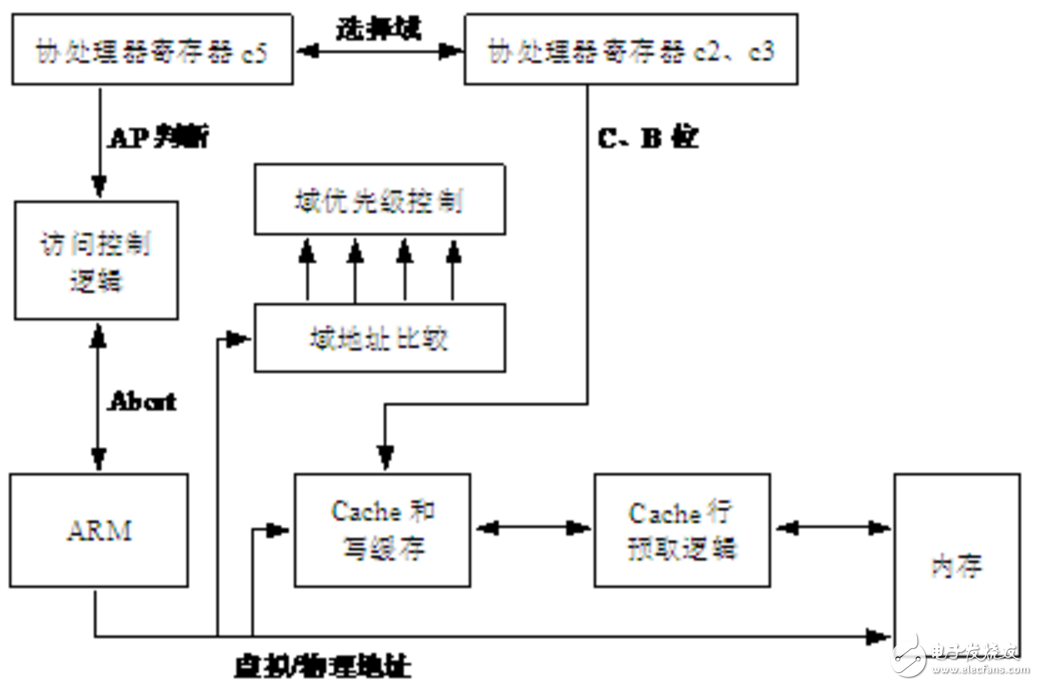

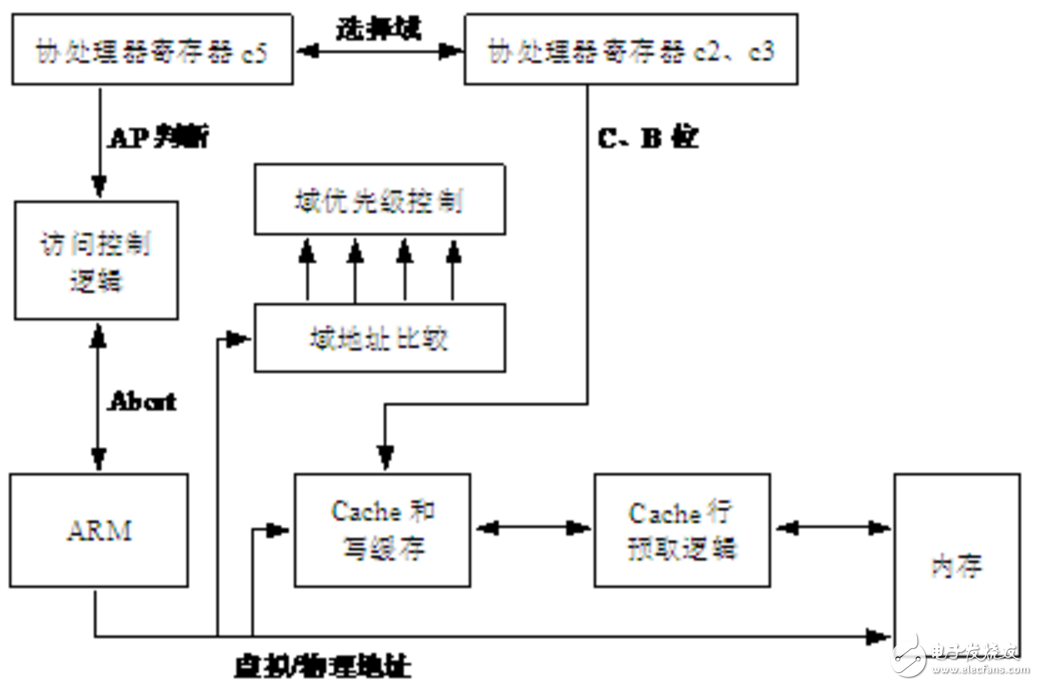

When the ARM processor attempts to access memory, the MPU checks if the address falls within a defined domain. If not, an exception is generated. For example, if the kernel is trying to fetch an instruction and the address is not mapped, a prefetch abort occurs. If it's a data access, a data abort is triggered instead.

If the address belongs to multiple domains, the MPU evaluates the priority of each domain to determine the correct access attributes. These attributes are configured via CP15 registers and include settings like Cache (C), Buffer (B), and Access Permission (AP).

- **C and B** control caching behavior, allowing for different policies such as write-back or cache-less access.

- **AP** defines the access rights, determining whether a domain is readable, writable, or inaccessible based on the current processor mode.

This mechanism ensures that only authorized processes can interact with specific memory regions, significantly enhancing system security and reliability.

When the ARM processor attempts to access memory, the MPU checks if the address falls within a defined domain. If not, an exception is generated. For example, if the kernel is trying to fetch an instruction and the address is not mapped, a prefetch abort occurs. If it's a data access, a data abort is triggered instead.

If the address belongs to multiple domains, the MPU evaluates the priority of each domain to determine the correct access attributes. These attributes are configured via CP15 registers and include settings like Cache (C), Buffer (B), and Access Permission (AP).

- **C and B** control caching behavior, allowing for different policies such as write-back or cache-less access.

- **AP** defines the access rights, determining whether a domain is readable, writable, or inaccessible based on the current processor mode.

This mechanism ensures that only authorized processes can interact with specific memory regions, significantly enhancing system security and reliability.

Active Professional Ktv Speaker,Top Speakers For Live Performance,Top Professional Performance Speakers,Portable Performance Speaker

NINGBO RFUN AUDIO TECHNOLOGY CO.,LTD , https://www.mosensound.com